NanoIC opent toegang tot allereerste fine-pitch RDL- en D2W-hybride bonding interconnect-PDK’s

Nieuwe geavanceerde interconnect-PDK’s effenen het pad voor chip-naar-chipintegratie met hoge dichtheid en energie-efficiëntie.

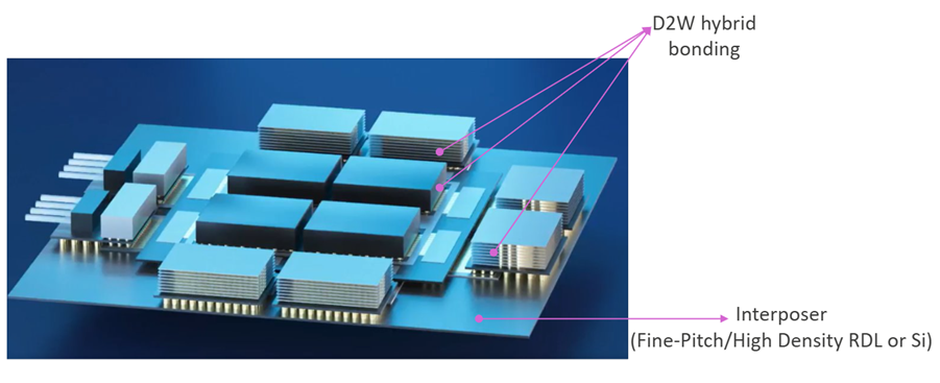

LEUVEN (België), 2 MAART 2026 — Vandaag introduceert de NanoIC-pilotlijn, een Europees initiatief gecoördineerd door imec en gericht op het versnellen van innovatie in chiptechnologieën voorbij 2 nm, twee geavanceerde interconnect process design kits (PDK’s) van een nieuwe generatie: een fine-pitch redistribution layer (RDL) en een die-to-wafer (D2W) hybride bonding PDK. Deze PDK’s met vroege toegang maken geavanceerde packagingmogelijkheden toegankelijk voor universiteiten, start-ups en industriële vernieuwers en vormen een belangrijke stap in het mogelijk maken van chip-naar-chipconnectiviteit met hoge dichtheid en energie-efficiëntie.

Nu de halfgeleiderindustrie evolueert naar steeds complexere en heterogene systeemarchitecturen, is advanced packaging een cruciale enabler geworden om deze vooruitgang te ondersteunen. In plaats van enkel individuele chips te verpakken, brengen hedendaagse packagingtechnologieën meerdere dies (chiplets) samen in sterk geïntegreerde systemen, waarbij prestaties, energie-efficiëntie en bandbreedte afhangen van hoe effectief deze componenten met elkaar communiceren. Door chiplets met hoge dichtheid te verbinden, vormt advanced packaging de basis voor de volgende generatie high-performance computing, AI-accelerators en data-intensieve toepassingen.

Om universiteiten, start-ups, mkb-bedrijven en industriële spelers in staat te stellen deze concepten om te zetten in praktische ontwerpen, brengt NanoIC vandaag de eerste versie uit van zijn fine-pitch redistribution layer (RDL) en die-to-wafer (D2W) hybride bonding process design kits (PDK’s). Deze PDK’s, ontwikkeld op de NanoIC-pilotlijn, bieden ontwerpers vroege toegang tot ontwerprichtlijnen en gevalideerde bouwblokken die nodig zijn om high-density chip-to-chipintegratie te verkennen.

Fine-pitch RDL PDK: high-density routing op polymeer-gebaseerde substraten

De fine-pitch redistribution layer (RDL) PDK introduceert een nieuwe manier om high-density chip-to-chipverbindingen te realiseren met polymeer-gebaseerde substraten. Traditioneel konden deze substraten geen extreem fijne lijnen ondersteunen, wat hun toepassing in advanced packaging beperkte. De technologie van imec, ontwikkeld binnen het NanoIC-project, doorbreekt deze beperking door uitzonderlijk kleine pitch-interconnects mogelijk te maken in een polymeer-gebaseerde RDL, met capaciteiten die verder gaan dan wat toonaangevende commerciële fabs vandaag bieden. Met lijnbreedtes en -afstanden tot 1,3 micron en microbump-pitches tot 20 micron geeft de RDL PDK ontwerpers toegang tot interconnects die de communicatiesnelheid met maximaal 40% kunnen verbeteren en het energieverbruik per bit met tot 15% kunnen verlagen, op een UCIe-Advanced die-to-die-interface. Hierdoor wordt fine-pitch RDL een aantrekkelijke integratieoptie voor een breed scala aan opkomende toepassingen, van automotive en high-performance computing tot next-generation GPU-architecturen.

D2W hybride bonding PDK: ultradichte die-to-die 3D-verbindingen

D2W hybride bonding voegt een tweede krachtige integratietechniek toe door uiterst compacte, directe verbindingen tussen dies in de derde dimensie mogelijk te maken. In plaats van traditionele koperbump-verbindingen vormt hybride bonding directe oxide-op-oxideverbindingen tussen de CMOS-die en de package-interface. Dit elimineert de parasitaire effecten die gepaard gaan met koperbumping en maakt communicatiepaden mogelijk met lage verliezen en hoge energie-efficiëntie.

Dankzij het vermogen om ultradichte chip-to-chipverbindingen met hoge bandbreedte te realiseren, is de D2W hybride bonding PDK bijzonder geschikt voor AI-toepassingen, geavanceerde computingplatformen en high-performance GPU-architecturen.

Een belangrijke stap richting volledige tape-outmogelijkheden

Met deze lancering wordt imec de eerste ter wereld die eenvoudig toegankelijke interconnect-PDK’s aanbiedt op deze integratieniveaus en dimensies. Deze initiële “exploratory version” biedt de essentiële tools die ontwerpers nodig hebben om de technologie te evalueren: systematische lay-outcreatie, geautomatiseerde en aangepaste routing en design rule checks.

“Deze eerste release is een pathfinding PDK,” legt Nicolas Pantano, hoofd van het demonstrator architect team bij imec, uit. “Het geeft onderzoekers, start-ups en bedrijven de essentiële tools om te starten met ontwerpen, ideeën te testen en feedback te geven. Naarmate de PDK’s verder rijpen, zullen ze evolueren van verkennende design kits naar complete, fabricage-klare toolsets met tape-outmogelijkheden, waarmee ontwerpers een lay-out die met deze PDK’s is gemaakt fysiek kunnen laten produceren op de pilotlijn, en hun concepten in silicium kunnen valideren in plaats van enkel in simulatie.”

Met de lancering van deze twee interconnect-PDK’s breidt NanoIC zijn aanbod uit tot in totaal vijf publiek toegankelijke process design kits. Na eerdere releases van de N2-, A14- en eDRAM-PDK’s markeert de introductie van de fine-pitch RDL- en D2W hybride bonding-PDK’s de volgende mijlpaal in de ontwikkeling van een complete beyond-2nm ontwerptoolkit, die logic, geheugen en nu ook interconnecttechnologieën omvat. Om hands-on verkenning te ondersteunen, organiseert NanoIC bovendien op 27 mei 2026 een speciale workshop over de RDL- en D2W-PDK’s. Alle praktische details zijn beschikbaar op de NanoIC-website.

Dit werk is mede mogelijk gemaakt door de NanoIC-pilotlijn. De aanschaf en exploitatie worden gezamenlijk gefinancierd door de Chips Joint Undertaking, via de programma’s Digital Europe (101183266) en Horizon Europe (101183277) van de Europese Unie, evenals door de deelnemende staten België (Vlaanderen), Frankrijk, Duitsland, Finland, Ierland en Roemenië. Voor meer informatie: nanoic-project.eu.